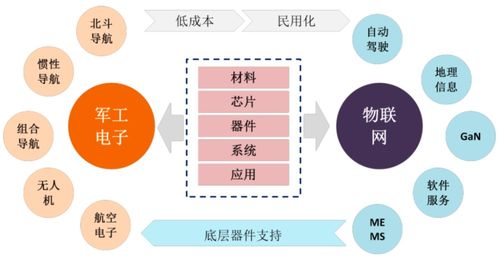

數(shù)字集成電路(Digital Integrated Circuit, IC)是現(xiàn)代電子設(shè)備的核心,廣泛應(yīng)用于計(jì)算機(jī)、通信系統(tǒng)和消費(fèi)電子產(chǎn)品中。其設(shè)計(jì)過(guò)程結(jié)合了電子工程、計(jì)算機(jī)科學(xué)和物理學(xué)等多個(gè)領(lǐng)域的知識(shí),旨在實(shí)現(xiàn)高效、可靠且低功耗的芯片。本文從多個(gè)角度透視數(shù)字集成電路設(shè)計(jì)的關(guān)鍵方面。

數(shù)字集成電路設(shè)計(jì)始于系統(tǒng)規(guī)范與架構(gòu)定義。設(shè)計(jì)團(tuán)隊(duì)需明確芯片的功能、性能指標(biāo)和功耗要求,確定整體架構(gòu),例如采用RISC或CISC處理器核心、存儲(chǔ)器層次結(jié)構(gòu)以及外設(shè)接口。這一階段通常涉及高級(jí)建模和仿真,以驗(yàn)證設(shè)計(jì)概念的可行性。

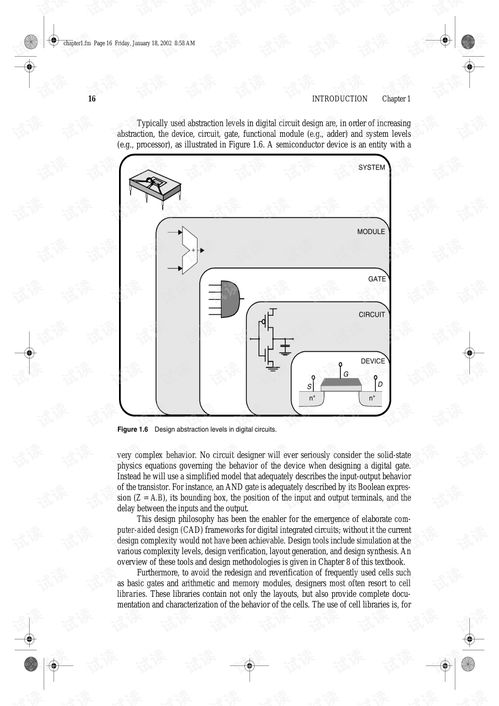

邏輯設(shè)計(jì)是核心環(huán)節(jié)。設(shè)計(jì)者使用硬件描述語(yǔ)言(如Verilog或VHDL)描述電路的邏輯功能,實(shí)現(xiàn)從門(mén)級(jí)到模塊級(jí)的抽象。通過(guò)邏輯綜合工具,將高級(jí)代碼轉(zhuǎn)換為門(mén)級(jí)網(wǎng)表,優(yōu)化時(shí)序和面積。這一過(guò)程注重邏輯正確性和性能預(yù)測(cè),例如時(shí)鐘頻率和延遲分析。

物理設(shè)計(jì)將邏輯網(wǎng)表映射到實(shí)際的硅片上。這包括布局規(guī)劃、單元放置、布線以及時(shí)序和功耗優(yōu)化。物理設(shè)計(jì)必須考慮制造工藝的限制,如線寬、層間連接和熱管理。工具如EDA(電子設(shè)計(jì)自動(dòng)化)軟件在自動(dòng)化布局和驗(yàn)證中發(fā)揮關(guān)鍵作用,確保設(shè)計(jì)符合設(shè)計(jì)規(guī)則。

驗(yàn)證和測(cè)試貫穿整個(gè)設(shè)計(jì)流程。通過(guò)仿真、形式驗(yàn)證和原型測(cè)試,設(shè)計(jì)者檢查功能錯(cuò)誤、時(shí)序違規(guī)和制造缺陷。隨著芯片復(fù)雜度的增加,驗(yàn)證已成為設(shè)計(jì)周期中最耗時(shí)的部分,需要采用先進(jìn)的測(cè)試向量和覆蓋率分析。

制造和封裝將設(shè)計(jì)轉(zhuǎn)化為實(shí)物。數(shù)字集成電路通常采用CMOS技術(shù)制造,涉及光刻、蝕刻和摻雜等步驟。封裝后,芯片需進(jìn)行最終測(cè)試,以確保在真實(shí)環(huán)境中的可靠性。

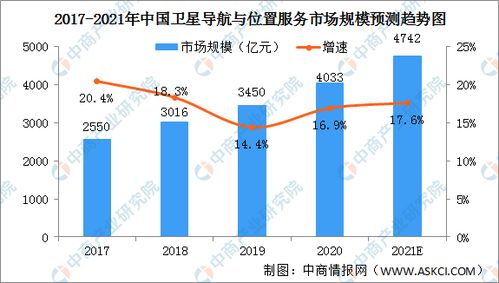

數(shù)字集成電路設(shè)計(jì)正面臨摩爾定律放緩的挑戰(zhàn),推動(dòng)著新技術(shù)的探索,如3D集成、AI加速設(shè)計(jì)和低功耗架構(gòu)。通過(guò)持續(xù)創(chuàng)新,數(shù)字IC設(shè)計(jì)將繼續(xù)驅(qū)動(dòng)電子行業(yè)的進(jìn)步,為智能社會(huì)奠定基礎(chǔ)。數(shù)字集成電路設(shè)計(jì)是一個(gè)多學(xué)科融合的復(fù)雜過(guò)程,其成功依賴(lài)于嚴(yán)謹(jǐn)?shù)牧鞒獭⑾冗M(jìn)的工具和跨團(tuán)隊(duì)協(xié)作。