隨著信息技術的飛速發展,專用集成電路(ASIC)已成為現代電子系統的核心。其中,CMOS組合邏輯設計作為集成電路設計的重要組成部分,廣泛應用于數字電路中。本文將深入探討CMOS組合邏輯的基礎原理、設計方法及其在集成電路中的實際應用。

一、CMOS組合邏輯基礎

組合邏輯電路是一種輸出僅依賴于當前輸入狀態的數字電路,不含存儲元件。在CMOS技術中,電路由互補的P型MOSFET和N型MOSFET構成,以低功耗和高噪聲容限著稱。基本CMOS組合邏輯門包括反相器(NOT)、與非門(NAND)、或非門(NOR)等,通過串聯和并聯MOSFET實現邏輯功能。例如,一個兩輸入NAND門由兩個并聯的PMOS和兩個串聯的NMOS組成,確保在輸入為高電平時輸出低電平,反之亦然。

二、CMOS組合邏輯設計方法

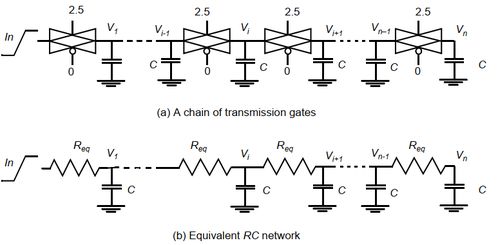

設計CMOS組合邏輯電路需遵循邏輯綜合和電路優化原則。設計者基于功能需求編寫布爾表達式或真值表,然后通過卡諾圖或邏輯簡化工具(如Espresso算法)最小化邏輯。將簡化后的邏輯映射到CMOS電路結構:

- 上拉網絡(由PMOS組成)實現邏輯函數的補形式,負責輸出高電平。

- 下拉網絡(由NMOS組成)實現原邏輯函數,負責輸出低電平。

設計時需考慮扇入、扇出、延遲和功耗等因素。例如,多輸入邏輯門可能因串聯MOSFET過多而增加延遲,因此常采用邏輯重組或緩沖器插入來優化性能。在先進工藝節點下,還需處理漏電流和電壓縮放問題。

三、集成電路設計中的實際應用

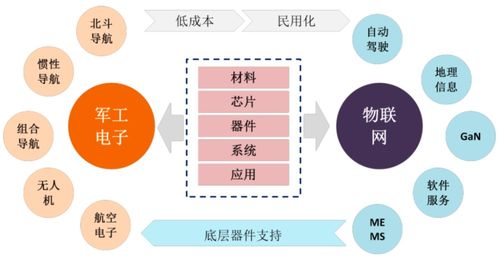

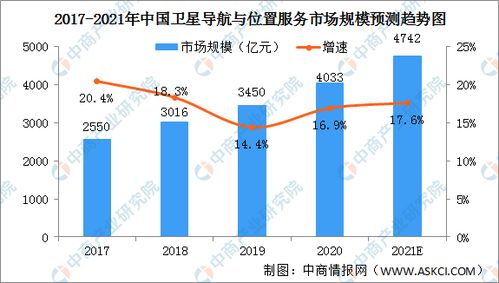

在專用集成電路設計中,CMOS組合邏輯用于構建算術邏輯單元(ALU)、數據路徑、控制單元等關鍵模塊。以ALU為例,它利用CMOS組合邏輯實現加法、比較等操作,通過精心設計門級電路來平衡速度和面積。在物理設計階段,布局布線工具將邏輯網表轉化為實際版圖,確保符合制造規則(如DRC和LVS)。隨著低功耗需求增長,技術如多閾值CMOS(MTCMOS)被引入,以動態控制電源,減少靜態功耗。

CMOS組合邏輯設計是專用集成電路的基石,其高效性和可靠性推動了從消費電子到高性能計算的發展。未來,隨著工藝進步和新興應用(如AI加速器)的涌現,CMOS設計將持續創新,結合3D集成和新型材料,進一步提升集成電路的性能與能效。